下面是由希赛小编提供的中级通信交换技术知识点精讲之时间(T型)交换器,希望对学友们有所帮助。具体内容如下:

时间(T型)交换器

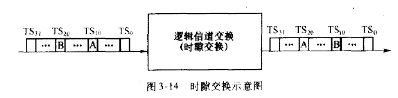

我们知道,在PCM时分复用一次群中,每一路基带信号占用帧内的一个时隙,且在每帧中都将占有相同编号的时隙。因此这种时分复用是以周期性帧内的时隙位置来区分各路信号的。由于帧周期和时隙宽度都是严格固定的,故称为同步时分复用。PCM-次群相当于提供了32条独立的64kbit/S信道。我们称这些信道为逻辑信道,时间交换器(TimeSwitch)正是要完成这些逻辑信道的相互交换,即实现信号由一个时隙至另一个时隙的搬移。如图3-14所示,在输人复用线上任意时隙的内容,经过交换可以在输出线上任一时隙输出。例如TS,。的内容被交换到TS2。,TSm内容被交换到TS,时隙内的内容就是数字话音信息,也就是8位PCM编码数字信息。所以时间交换器实质上是实现时隙交换,也就是完成时隙内容的搬移。

时间交换器又称为T型交换器,其功能是完成一条PCM复用线上各时隙内容的交换。从理论上讲,任何延时器件都能完成时隙交换,但这里不同输人时隙要求交换后的输出时隙不同,而且是经常变化的,因此,要求对任一时隙的延时长度必须易于控制。如将一次群信号中每一帧的第5时隙的内容延时一个时隙(3.9#)后输出,即把TS5的内容交换到TS6。如果将第2时隙的内容延时31个时隙,即搬移到下一帧的第1时隙,也就是把TS2W内容交换到TS。在实际应用中,这种延时几乎都是利用随机存储器(RAM)来实现的。

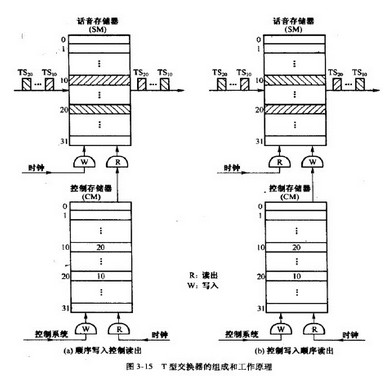

时间交换器主要由话音存储器(SM)和控制存储器(CM)组成,如图3-15所示。话音存储器用来存储数字话音信息,以便延时。话音存储器的单元数等于输入复用线上每帧内的时隙数,每个单元的位数都是8位,正好存储每个时隙的8位数字话音编码。控制存储器是用来存储话音时隙地址的,以便控制延时。控制存储器的单元数与话音存储器的单元数相同,但位数由SM的单元数决定,如一次群的T型交换器的CM为5位,25=32,即可寻址整个SM。

对话音存储器的控制有两种方式:一种是“顺序写人,控制读出”,如图3-15(a)所示;另一种是“控制写入,顺序读出”,如图3-15(b)所示。这里所谓“顺序”,是指由时钟电路癍供SM的读或写地址,它能使SM的单元号与输出或输入复用线上的时隙号相对应。而“控制”是指按控制存储器中已规定的内容来控制话音存储器的读或写,时隙交换就是在这里控制延时的。对控制存储器的控制方式总是由交换控制系统控制写人,然后按顺序读出。控制系统根据呼叫要求,得到对CM进行写人操作的地址和数据,这里完成了写入操作就是完成了接线。

下面以两个用户之间要求通话为例,说明时间交换器的工作原理。假定用户A占用了TS)0,用户B占用了TSm,两个用户要实现通话,就必须把TS,。时隙中的内容交换到TSm,同时把TSm的内容交换到TS,。。经过分析,控制系统会在CM的10号单元写人20:20号单元写人10。在图3-15(a)中,话音存储器是顺序写入,输人复用线上的各个时隙的内容顺序写人到SM的相应单元,如TSID的内容写人到SM的10号单元,朽的内容写人到SM的20号单元。话音存储器由CM控制读出,在TS,。时刻,CM输出20,控制将SM的20号单元中的内容读出,即输出到了TSW,因而完成了从的交换。同理,在TSM时刻,CM输出10,控制将SM的10号单元中的内容读出,即输出到了TS&则完成了从TS,。到交换。在图3-15(b)中,话音存储器是由CM控制写人显然在TS。时刻,CM输出20,控制将TS。的内容写人到了SM的20号单元,同理将朽^的内容写人到了SM的10号单元。SM按顺序读出,10号单元的内容输出到TS。但SM的10号单元写人的是的内容,这样就完成了从TSjTS,。的交换,同理可以完成从TS。到TSM的交换。

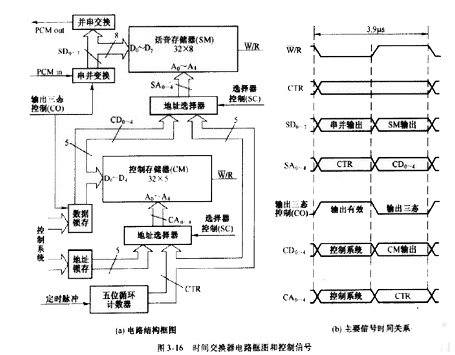

上面讨论了时间交换器的组成和工作原理,除了话音存储器和控制存储器,时间交换器的组成电路中还包括:串并变换电路、并串变换电路、计数器及其他控制电路。时间交换器中既有组合逻辑电路也有时序电路,图3-16给出了PCM-次群时间交换器的电路框图和主要控制信号的时间关系。

在图3-16中,根据给出的信号时间关系,可以看出时间交换器采用了“顺序写人、控制读出”方式。由于存储器的数据线是双向的,串并变换电路和控制系统的数据锁存器的输出必须是三态的。在一个时隙内,对SM要进行一次写操作和一次读操作,读和写分别是对不同单元操作的,地址选择器提供相应的操作地址。此外,串并变换电路和并串变换电路各产生一个时隙的固有延时,必须在实际设计中加以考虑。

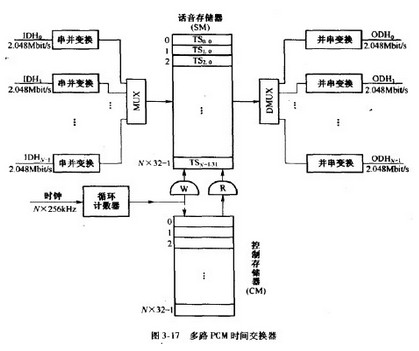

现在来讨论多路PCM-次群的时间交换器,它要完成不同PCM一次群信号中各时隙之间的交换。一个能实现A1路PCM交换的时间交换器如图3-17所示,输人时分复用线用IDHInputDigitalHighway)表示,即IDHo,IDH,1DHV.10输出时分复用线用ODH(OutputDigitalHighway)表示,即ODH。,ODH,,…,ODHWM。输人的况路一次群信号经串并变换及多路复用后,形成8线并行的输出。如果将1DH,的第)时隙记着TSy,则多路复用后的输出依次为:TSTSyTSq/TS^TSy。串并变换和复用原理如图3-18所示。多路交换的时间交换器和单路交换的原理相同,但这里的话音存储器(SM)的容量为32x8位,控制存储器(CM)的容量为/Vx32x(log^+5)位,输人输出时隙速率为Nx256kHz,循环计数器的位数为5+log2AT。如果话音存储器按“顺序写入,控制读出”方式工作.则IDH,时隙的内容写人到SM的第ATxy+i单元。

从话音存储器读出的各时隙内容,经解复用器(DMUX)和并串变换电路,使它恢复为原来的复用度和速率,解复用器的组成框图与图3-18所示的复用器的组成框图对应,完成相反的操作,这里不再赞述。

时伺交换器还可以设计成集中型或扩张型,如果话音存储器的写人速率高于读出速率,则可以得到时间集中器。如果话音存储器的写入速率低于读出速率,可以得到时间扩张器。

目前,已经有一些中、小容量的VLSI数字交换器专用芯片,如MITEL公司的MT8980D,它能完成8路PCM30/32信号的交换,有兴趣的读者可查阅有关手册。时间交换器的容擞主要受到存储器读写速率的限制,一般存储器完成一次读写操作的时间约在几十到几百纳秒(ns)之间,因此,单个时间交换器的容量通常不超过1024话路(32路一次群)。当输人一次群的路数超过单个时间交换器的容量极限时,必须使用多个时间交换器,而不同时间交换器之间的交换需要通过空间交换器来完成。

相关推荐: