考研408计算机统考分两部分,80分单项选择题和70分大题,满分150分。单项选择题总共80分,每小题2分,40小题。单项选择题,1-10题是数据结构部分;11-22题是计算机组成原理部分;23-32题是操作系统部分;33-40题是计算机网络部分。综合应用题70分,共7小题,41和42题是数据结构题,分值各为10分和15分;43和44题是计算机组成原理题,各占8分和13分;45和46题是操作系统题,各占7分和8分;47题是计算机网络题,分值为9分。为了方便大家更好的来备考,小编为大家整理了“2022年408计算机考研真题”,希望可以帮助大家更好的复习408计算机考研内容。

2022年考研408计算机统考考研真题

二、综合应用题(第41~47小题,共70分)

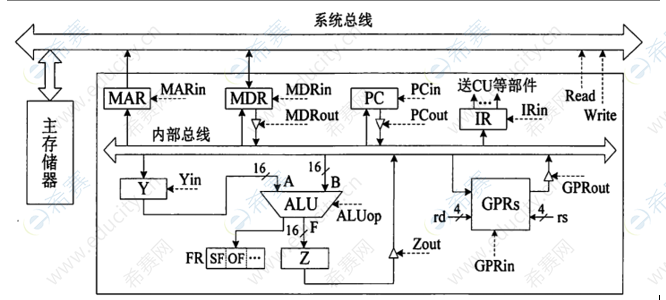

43、(15分)某CPU中部分数据通路如图所示,其中,GPRs为通用寄存器组;FR为标志寄存器,用于存放ALU产生的标志信息;带箭头虚线表示控制信号,如控制信号Read、Write分别表示主存读、主存写,MDRin表示内部总线上数据写入MDR,MDRout表示MDR的内容送内部总线。

(1)ALU的输入端A、B及输出端F的最高位分别为A15、B15及F15,FR中的符号标志和溢出标志分别为SF和OF,则SF的逻辑表达式是什么?A加B、A减B时OF的逻辑表达式分别是什么?要求逻辑表达式的输入变量为A15、B15及F15。

(2)为什么要设置暂存器Y和Z?

(3)若GPRs的输入端rs、rd分别为所读、写的通用寄存器的编号,则GPRs中最多有多少个通用寄存器?rs和rd来自图中的哪个寄存器?已知GPRs内部有一个地址译码器和一个多路选择器,rd应该连接地址译码器还是多路选择器?

(4)取指令阶段(不考虑PC增量操作)的控制信号序列是什么?若从发出主存读命令到主存读出数据并传送到MDR共需5个时钟周期,则取指令阶段至少需要几个时钟周期?

(5)图中控制信号由什么部件产生?图中哪些寄存器的输出信号会连到该部件的输入端?

44、假设某磁盘驱动器中有4个双面盘片,每个盘面有20000个磁道,每个磁道有500个扇区,每个扇区可记录512字节的数据,盘片转速为7200r/m(转/分),平均寻道时间为5ms,请回答下列问题。

(1)每个扇区包含数据及地址信息,地址信息分为3个字段,这3个字段的名称格式什么?对于该磁盘,各字段至少占多少位?

(2)一个扇区的平均访问时间约为多少?

(3)若采用周期挪用DMA方式进行磁盘与主机之间的数据传送,磁盘控制器中的数据缓冲区大小为64位,则在一个扇区读写过程中,DMA控制器向CPU发送了多少次总线请求?若CPU检测到DMA控制器的总线请求信号时也需要访问主存,则DMA控制器是否可以获得总线使用权?为什么?

相关推荐:

| 课程名称 | 课程价格 | 课程链接 |

| 2026写作备考攻略 | 免费 | 点击试听 |

| 2010-2025数学16套真题讲解 | 免费 | 点击试听 |

| 考研【公共课】自学视频教程 | 98元 | 点击试听 |

| 408计算机】考研自学视频教程(真题+习题+考点) | 98元 | 点击查看 |

| 管理类联考数学基本功视频教程 | 398元 | 点击查看 |

扫码直达>>>考研课程咨询

| ||